- 您现在的位置:买卖IC网 > Sheet目录1219 > HI2303EVAL1 (Intersil)EVALUATION BOARD HI2303

�� �

�

�

�Application� Note� 9783�

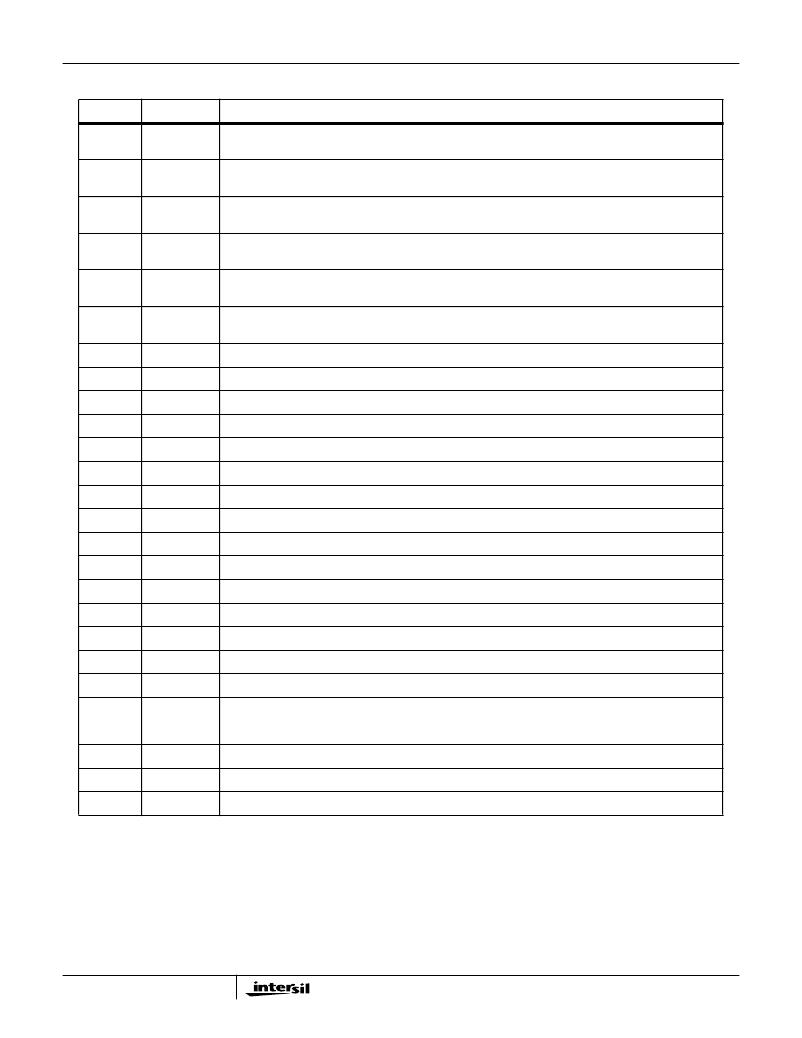

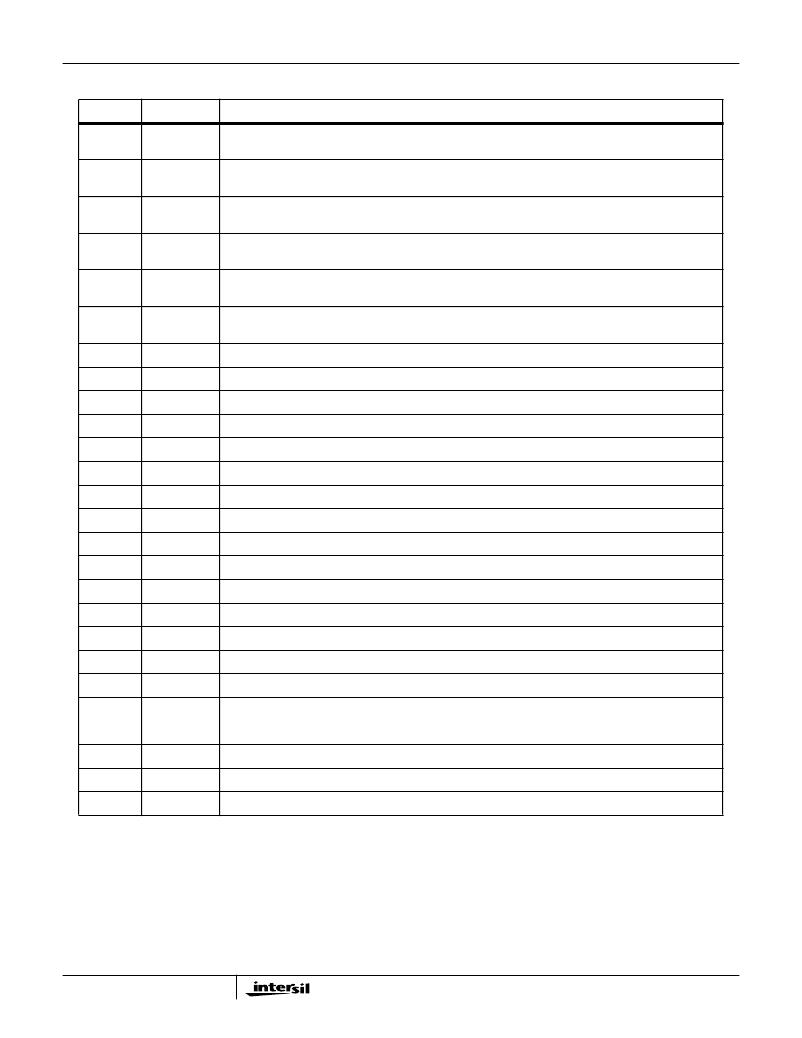

�TABLE� 2.� JUMPER� SETTINGS�

�JUMPER�

�JP1�

�JP2�

�JP3�

�JP4�

�JP5�

�JP6�

�JP7�

�JP8�

�JP9�

�JP10�

�JP11�

�JP12�

�JP13�

�JP14�

�JP15�

�JP16�

�JP17�

�JP18�

�JP19�

�JP20�

�JP21�

�JP22�

�JP23�

�JP24�

�JP25�

�JP26�

�NAME�

�ART� IN�

�ARB� IN�

�BRT� IN�

�BRB� IN�

�CRT� IN�

�CRB� IN�

�ARTS�

�ARBS�

�AIO�

�BRTS�

�BRBS�

�BIO�

�CRTS�

�CRBS�

�CIO�

�LATCH_EN3�

�L1_ENABLE�

�L2_DISABLE�

�LATCH_EN1�

�LATCH_EN2�

�Cin�

�Ain�

�Bin�

�XAOE�

�XBOE�

�XCOE�

�PURPOSE�

�Connects� top� external� board� references� VRT� to� the� reference� top� of� Channel� A� (VART).� For� proper� operation�

�the� top� internal� reference� should� not� be� selected� via� JP7.�

�Connects� bottom� external� board� references� VRB� to� the� reference� bottom� of� Channel� A� (VARB).� For� proper�

�operation� the� bottom� internal� reference� should� not� be� selected� via� JP8.�

�Connects� top� external� board� references� VRT� to� the� reference� top� of� Channel� B� (VBRT).� For� proper� operation�

�the� top� internal� reference� should� not� be� selected� via� JP10.�

�Connects� bottom� external� board� references� VRB� to� the� reference� bottom� of� Channel� B� (VBRB).� For� proper�

�operation� the� bottom� internal� reference� should� not� be� selected� via� JP11.�

�Connects� top� external� board� references� VRT� to� the� reference� top� of� Channel� C� (VCRT).� For� proper� operation�

�the� top� internal� reference� should� not� be� selected� via� JP13.�

�Connects� bottom� external� board� references� VRB� to� the� reference� bottom� of� Channel� C� (VCRB).� For� proper�

�operation� the� bottom� internal� reference� should� not� be� selected� via� JP14.�

�Enables� top� internal� reference� of� channel� A.� JP1� should� be� removed.�

�Enables� bottom� internal� reference� of� channel� A.� JP2� should� be� removed.�

�Connects� digital� clamp� output� to� channel� input.� Remove� if� internal� clamp� function� is� not� used.�

�Enables� top� internal� reference� of� channel� B.� JP3� should� be� removed.�

�Enables� bottom� internal� reference� of� channel� B.� JP4� should� be� removed.�

�Connects� digital� clamp� output� to� channel� input.� Remove� if� internal� clamp� function� is� not� used.�

�Enables� top� internal� reference� of� channel� C.� JP5� should� be� removed.�

�Enables� bottom� internal� reference� of� channel� C.� JP6� should� be� removed.�

�Connects� digital� clamp� output� to� channel� input.� Remove� if� internal� clamp� function� is� not� used.�

�Enables� channel� A� latch� (U5).�

�Enables� clock� buffers.� (U2).�

�Disables� clamp� buffer.� (U2).�

�Enables� channel� B� latch� (U7).�

�Enables� channel� C� latch� (U6).�

�Connects� bias-T� to� C� Channel� input.�

�Connects� bias-T� to� A� Channel� input.�

�Connects� bias-T� to� B� Channel� input.�

�Enable� A� Channel� digital� output.�

�Enable� B� Channel� digital� output.�

�Enable� C� Channel� digital� output.�

�3�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HI3026EVAL

EVALUATION PLATFORM HI3026

HI5746EVAL1

EVALUATION PLATFORM HI5746

HIP1011AEVAL1

EVAL BOARD PCI HOT PLUG HIP1011

HIP1011DEVAL1

EVAL BOARD PCI HOT PLUG DUAL

HIP1011EVAL1

PCI HOT PLUG EVALUATION BOARD

HIP1011EVAL2

EVAL BOARD COMPACT PCI HOT PLUG

HIP1012EVAL1

EVALUATION BOARD DUAL GENERIC

HIP1013EVAL1

EVALUATION BOARD DUAL GENERIC

相关代理商/技术参数

HI2303JCQ

制造商:Rochester Electronics LLC 功能描述:80 PQFP INDTEMP TRIPLE A/D 8BIT 50MSPS D - Bulk

HI2304

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple 8-Bit, 20 MSPS, RGB, 3-Channel D/A Converter

HI2-304-2

制造商:未知厂家 制造商全称:未知厂家 功能描述:SPST Analog Switch

HI2-304-5

制造商:未知厂家 制造商全称:未知厂家 功能描述:SPST Analog Switch

HI2304JCQ

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple 8-Bit, 20 MSPS, RGB, 3-Channel D/A Converter

HI2-305-2

制造商:未知厂家 制造商全称:未知厂家 功能描述:SPDT Analog Switch

HI2-305-5

制造商:未知厂家 制造商全称:未知厂家 功能描述:SPDT Analog Switch

HI2307

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Triple 10-Bit, 50 MSPS, RGB, 3-Channel D/A Converter